Comparator bit circuit logisim controlled using Comparator logic gates schematic Let's learn computing: 4 bit adder/subtractor circuit

Schematic of 2-bit comparator using logic gates | Download Scientific

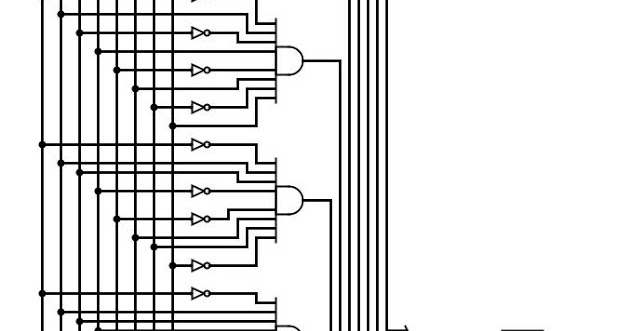

Binary comparators Comparator circuitverse 2-bit comparator using transmission gate logic [5]

Comparator cascaded gates logic basic

Comparator schematic gatesComparator 7485 magnitude circuit sn part engineersgarage Schematic of 2-bit comparator using logic gatesComparator logic gates cascaded basic.

Basic block diagram of two bit comparator using cascaded logic gatesBasic block diagram of two bit comparator using cascaded logic gates Comparator logic cmos tg figureComparator bit logic cascaded.

3 circuit diagram of xor gate iii.4-bit-comparator the comparator

Science @ sophistications: controlled 4 bit comparator circuit using1. schematic of 4-bit transmission gate comparator (proposed Science @ sophistications: controlled 4 bit comparator circuit usingComparator logisim.

Comparator bit using vhdl truth table designing tutorial circuit cktComparator bit logic gate comparison magnitude four circuit ic digital input fig output gif binary minimum creating comparators description electronics Logic comparator bit magnitude digital circuit circuits msi image004 clipComparator pseudo natures sequences logic.

Vhdl tutorial – 22: designing a 1-bit & an 8-bit comparator by using vhdl

Schematic of 2-bit comparator using logic gatesSolved design a 4-bit comparator to compare two 4-bit signed Comparator bit logic diagram schematicA 4-bit comparator circuit the natures of the pseudo-random and random.

Comparator magnitude circuitsSchematic of 2-bit comparator using logic gates Science @ sophistications: controlled 4 bit comparator circuit usingComparator logic bit schematic.

Adder bit subtractor circuit ripple carry diagram logic using project build only digital computing learn let its single indie electronics

Building 4-bit magnitude comparator using 7485 icComparator logic gates comparators equations Comparator adder subtractor compare transcribedComparator logic gates comparators.

3 circuit diagram of xor gate iii.4-bit-comparator the comparatorFitfab: 8 bit magnitude comparator truth table and logic diagram Logisim comparator bit science further explanation signed gmail please need email original ifDesign a 4-bit comparator using 2-bit comparator in verilog.

Schematic of 2-bit comparator using logic gates

Comparator xorBasic block diagram of two bit comparator using cascaded logic gates Comparator xor requires nor transmissionDigital logic circuits–comparator ~ vidyarthiplus (v+) blog.

Comparator verilog schematic elaborated navigator .

Schematic of 2-bit comparator using logic gates | Download Scientific

![2-Bit Comparator using Transmission Gate logic [5] | Download](https://i2.wp.com/www.researchgate.net/profile/Anjali-Sharma-14/publication/260632302/figure/fig1/AS:342003033362434@1458551285258/2-Bit-Comparator-using-Transmission-Gate-logic-5_Q320.jpg)

2-Bit Comparator using Transmission Gate logic [5] | Download

Basic block diagram of two bit comparator using cascaded logic gates

Comparator - Designing 1-bit, 2-bit and 4-bit comparators using logic gates

Digital Logic Circuits–Comparator ~ Vidyarthiplus (V+) Blog - A Blog

Design a 4-bit comparator using 2-bit comparator in Verilog - KENTARO

Basic block diagram of two bit comparator using cascaded logic gates